ARM preps enterprise assault with speedy on-chip network

ARM has detailed two technologies to help move its chips into enterprise servers, currently dominated by Intel.

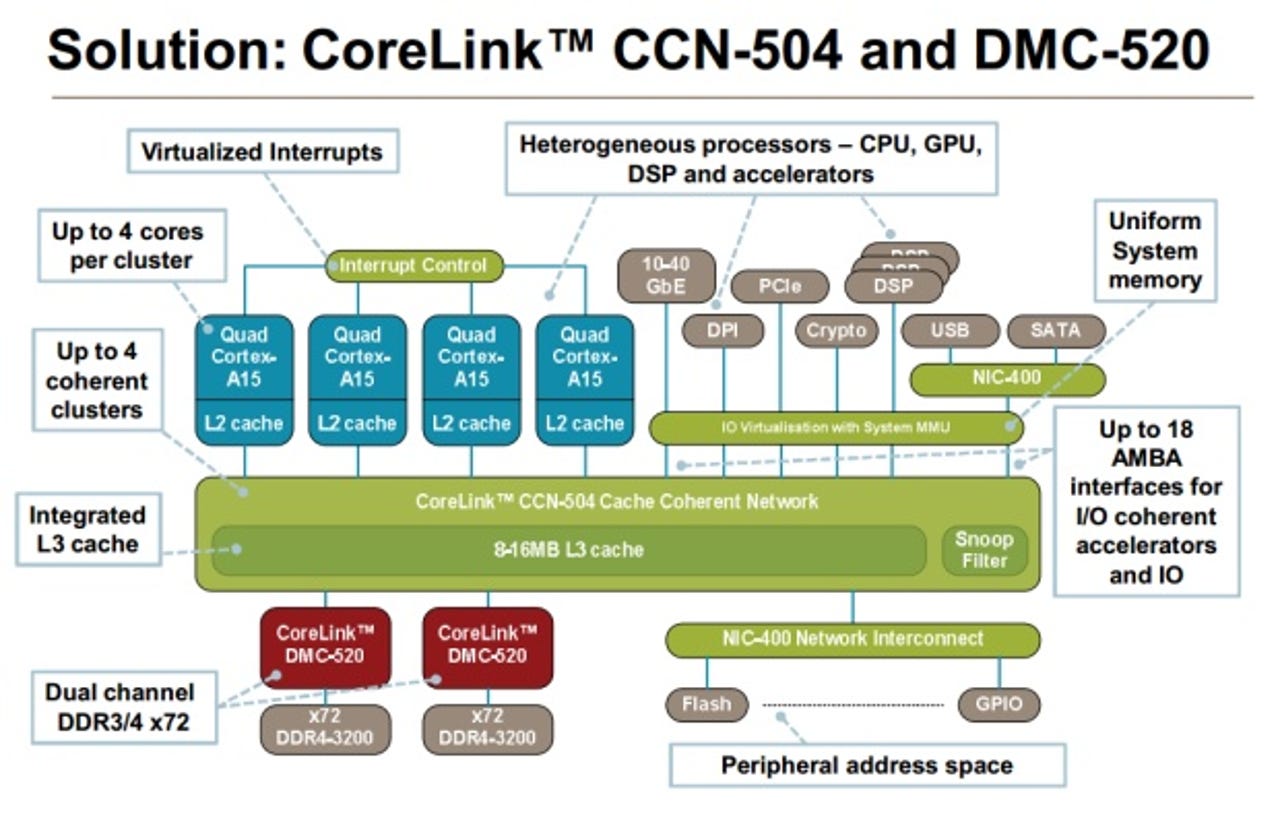

The ARM CoreLink CCN-504 cache coherent network and CoreLink DMC-520 dynamic memory controller technologies, announced on Wednesday, see the Cambridge, UK-based low-power chip designer add greater trans-core bandwidth and support for new memory technologies.

ARM says this makes its chips a better fit for parallel workloads and multi-core operating systems, while giving them support for upcoming memory technologies likely to be used in enterprise servers.

"You wouldn't see this in a mobile phone... it's focused very much on what we call enterprise applications," Neil Parris, an interconnect product manager at ARM, said. "With this kind of product scaling up to 16 cores, this is really opening up new areas for ARM."

Over the past year the company has added features to its chips to make them better candidates for going into high-end datacentre gear, which has traditionally been dominated by x86 chips from Intel and AMD, and, to a lesser extent, processors from Oracle, Fujitsu and IBM.

The first move was the 64-bit ARM v8 chip design, with a large memory space for modern datacentre use. Along with this, it inked a deal with chip fabricator TSMC to jointly develop new ways of building chips on more finely detailed processes.

Trans-core bandwidth

The CCN-504 technology lets ARM give its chips a terabit of on-chip trans-core bandwidth. It supports ARM's A-15 and upcoming 64-bit capable ARM v8 chip designs, initially up to 16 cores, though this could increase in the future, Parris said. ARM server specialist Calxeda is listed as a lead licensee of the technology, along with storage and networking specialist LSI.

By adding greater trans-core bandwidth, the company aims to make it easier for applications and operating systems that support parallel processing to get the most out of its chips.

"We've designed the fundamental microarchitecture of the interconnect so there's no specific hotspot and bottleneck," Parris said. "We expect very much to have parallel processing between the different CPU clusters."

"We expect very much to have parallel processing between the different CPU clusters" — Neil Parris, ARM

Many operating systems support SMP, symmetric multiprocessing, a feature that lets them split their work across multiple cores. By using this technology, the operating system "is effectively going to try and load balance the tasks across the available resources and available cores", Parris said.

Because of this, with the update ARM's chips are capable of supporting both general purpose server workloads, and parallel-specific tasks such as MemcacheD, to a greater extent than before.

As ARM only designs its chips and does not make them, it is up to partners to fabricate the licensed processors. Prototype silicon should be available in 2013 and partners should be able to ramp up production in early 2014, Parris said. Internally, ARM has been working with the chips on a 28nm process, though this could change in the future he said.

Along with CCN-504 the company also announced DMC-520, supporting next-generation server memory systems like DDR3, DDR3L and DDR4 DRAM.

This adds support for ECC (error correction code) and for the above mentioned memory technologies, which are the "kind of features needed in storage applications", Parris said.