Inside Intel's Prescott

Cheaper to make

One of the most important aims for Intel is to reduce costs, and the company will see an immediate benefit from Prescott's most fundamental innovation -- the 90-nanometre (nm) process. The current generation of Northwood Pentium 4s are fabricated in a 130nm process, giving the chips themselves a die size 140 square millimetres. By contrast, Prescott chips are 112 mm square, meaning many more can be made per wafer. Intel has already moved to larger wafers that, combined with the smaller die size, should produce around four times as many chips per wafer as before. The company never comments on its actual cost per chip, but Prescott will be substantially cheaper to make than previous Pentium 4s.

Speeds and feeds

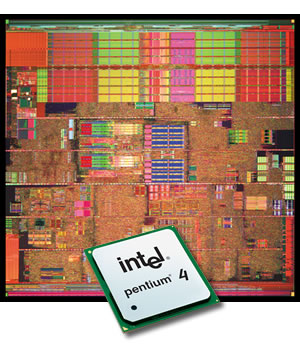

Although smaller processes have the potential to go faster than larger ones (put crudely, fewer electrons have to be shunted around each logical element), the Prescott range at launch tops out at 3.4GHz (new 3.4GHz versions of Northwood Pentium 4 and Pentium 4 Extreme Edition are also being launched at the same time). It will scale up to at least 5GHz over time: Intel has introduced strained silicon -- where the material is stressed to align the molecules and ease the passage of electrons through the matrix -- and replaced the old cobalt silicide chemistry with nickel silicide, which also reduces electrical resistance. Layout of the chip's major subsystems is radically different: automated reshuffling of the computational units, buses and control logic in order to improve clock distribution around the chip has meant that not all logically linked functions are in the same physical area.

Prescott's major performance enhancer is larger cache: 1MB of Level 2 cache, 16KB of Level 1 data cache and an instruction cache capable of storing 12k micro-ops: as with previous Pentiums, the chip translates Pentium machine code into its internal instruction set before executing them. It's the management of these micro-ops that most concerns the chip designers: Prescott has a pipeline half as long again as Northwood's 20 stages, which accelerates program execution most of the time but carries a severe performance penalty if the chip mistakenly loads in a chunk of code that unexpectedly transfers control outside the pipeline. When that happens, the chip has to empty the pipeline and refill it -- the longer the pipeline, the longer this takes. This factor means that for some code Prescott will be slower than Northwood, clock for clock, but that at higher speeds -- probably around 4GHz -- the new chip will be more efficient.

On top of Northwood’s complement of SSE2 instructions, Prescott has an extra 13 PNI (Prescott New Instructions) commands. Most of these are concerned with matrix mathematics of the sort used in video, graphics and signal processing -- a small set of improvements that round out the processor's feature set with an eye to future multimedia applications. More interestingly, Intel has included two process synchronisation commands: MONITOR and MWAIT. MONITOR sets up an area of memory that the processor's hardware will watch for a signal, while MWAIT tells the processor that it can temporarily suspend the process, thread or logical processor that issued it. These commands -- which may grow to a family of synchronisation methods in future processors -- can be useful in optimising virtual processor, multiprocessor and hyperthreaded programs. However, it, like the rest of the PNI commands, will only be useful when software is rewritten: there'll be no effect on existing programs.

Hidden features

Although Intel won't be drawn on the reports, it is thought that Prescott may contain other technology to be enabled at a later date -- much as hyperthreading was shipped disabled in earlier Pentium 4s before it was announced. Intel's security system, LaGrande, was due to be in, and enabled in, Prescott, but Intel later amended that to say the circuitry would be present but not enabled until future editions of the chip -- possibly in 2005 or later. Intel has been much more circumspect about rumoured 64-bit extensions (the so called Yamhill project), although AMD's success in promoting 64-bit operating system modifications may have persuaded Intel to accelerate its development.

Externally, Prescott looks very similar to existing Pentium 4s: an 800 MHz frontside bus, around 100 Watts of heat dissipation -- Intel says that existing heatsinks should be adequate -- and an mPGA478 package. The switch from Northwood to Prescott should be swift, as the company is labelling and packaging the new chips to take over as seamlessly as possible. However, the real benefits from the new architecture should come later, as the clock speed is ramped up and new features are enabled.