Inside Intel's Napa platform

The launch of Intel's new Napa platform brings with it Yonah, the company’s first dual-core mobile processor. Now more properly named the Intel Core Duo, Yonah is an evolution of the Pentium M processor. As it's also expected to find its way into low-power blade servers and the like, there’s no M or Mobile in the processor name: the next generation of this architecture, codenamed Merom, will move further into full-blown desktop (Conroe) and server (Woodcrest) configurations.

Core facts

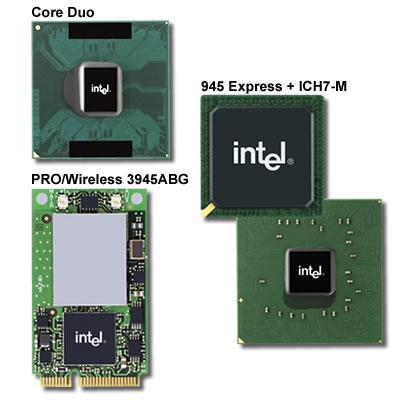

Intel’s nomenclature takes a bit of work to decode. The Napa platform is officially called Centrino Duo, which includes the Mobile Intel 945 Express chipset, the Intel PRO/Wireless 3945ABG Wi-Fi PCI Express MiniCard and the Intel Core Duo processor. A low-cost version of the platform built around a single-core Yonah -- why throw away a faulty chip if only half has failed? -- is simply called Centrino as before, although the processor chip itself is labelled the Intel Core Solo.

Yonah's two cores are functionally identical mirror images of each other, which simplifies the routing of common signals between them. Apart from duality, Yonah's biggest -- or smallest -- change is its architectural feature size, shrunk to 65nm from its predecessor Dothan's 90nm. This smaller size keeps the processor line in track with the precepts of Moore’s Law, and gives the designers more room to trade off performance against power consumption. Intel claims that Yonah has twice and Merom will have three times the integer performance per watt of Banias, the 130nm mobile chip that kicked off this line of designs.

| Napa and Sonoma platforms compared | ||

| Platform | Sonoma (2005) | Napa (2006) |

| CPU | Dothan (single core, 90nm) | Yonah (dual core, 65nm) |

| Frontside bus (FSB) | 533MHz | 667MHz |

| Wireless | 2915ABG (Mini-PCI) | 3945ABG (MiniCard) |

| Memory | DDR2 (400/533MHz) | DDR2 (533/667MHz) |

| Chipset | 915 & ICH6-M | 945 & ICH7-M |

| ODD | Parallel ATA | Serial ATA |

| Graphics | GMA900 | GMA950 |

| Ethernet | Integrated 10/100 (based on PCIe) | Integrated 10/100/1000 (based on PCIe) |

| Audio | Intel High Definition Audio | Intel High Definition Audio |

Lower power consumption

Power consumption has been a big issue in Yonah's creation. A lot of attention has been paid to the leakage current -- the power taken when the chip isn’t doing any processing at all. Although this is typically a few billionths of a watt per transistor, with 151 million transistors it becomes a major issue. Various techniques can improve the situation, such as switching off power altogether to idle areas of the chip and changing the transistor geometry and composition to improve the insulation between its components. Intel says that it's now designing for power consumption in the same way that it has always designed for minimal chip area and most effective timing, but that deciding to do this came about almost by accident: it found big power advantages while designing for aggressive area reduction just as the market started to worry about watts.

The cores themselves have a complex series of power saving options: Active, Halt, Clock Stopped, Sleep, Deeper Sleep and Enhanced Deeper Sleep, which successively push the chip deeper into a coma from which it takes successively longer to return. Each core can slip into the appropriate mode independently of the other; dynamic power management also watches the frequency and power trade-offs for portions of the cores. The cores can finesse their frequencies as appropriate, but don’t have independent voltage control; Intel says it looked at this, but that the form factors for multiple off-chip voltage regulators and the complications caused by routing split high-quality power feeds across the circuit board made this an unappetising option.

Off-chip factors haven’t been ignored. More precise thermal monitoring of hotspots on the chip should mean that power isn’t wasted spinning the cooling fan before it's needed. The chipset can also be safely powered down when the CPU is asleep through a process rather cutely called Dynamic Bus Parking. The chipset itself can abandon main memory to self-refresh mode during enhanced deeper sleep; it can minimise the amount of memory accessed by the display, dim the backlight automatically and compensate by lightening the LCD’s pixels, and read an external sensor to reduce the brightness when the computer is being used in low light levels.

Cleverer cache

Back in the CPU, the Level 2 cache is a major part of Yonah’s design. The 2MB of L2 cache is dynamically allocated between the two cores -- the busier core gets more cache. If one core is idle, the whole of the L2 cache becomes available to the other; if both cores are idle, then the cache can go into one of a number of sleep modes, including one where some or all of the data is written out to main memory and some or all of the cache is physically turned off. Improvements to the caching algorithms and deeper write buffers also reduce expensive main bus traffic, which would otherwise reduce performance and increase power consumption.

Both cores share a single bus into the cache, and data that's shared between processes on different cores can be accessed by either core without creating main bus traffic. This is unlikely to be much of an issue in typical notebook use, but is an example of an architectural feature that may become more important as the chip design filters into servers. It also compensates somewhat for the lack of a dedicated interprocessor bus.

Yonah has some good old-fashioned logic and arithmetic improvements too. It can bundle more instructions together for simultaneous handling -- both ordinary and SSE multimedia -- and do some operations in one micro-op that took four before. It’s got deeper pipelining in the floating-point multipliers and more intelligent integer dividers that can do 32-by-32-bit divides in between a half and a quarter of the cycles required by the previous chip. Intel says that software profiling suggests that a lot of divisions will be helped by this: it might be a peculiarly obscure part of the chip’s design, but the engineers are rather proud of it. Finally, there are more integer arithmetic units and ten new SSE3 instructions for media handling. In all, a fairly respectable smorgasbord of minor novelties that should lift overall performance across the board.

Yonah's designers are keen to emphasise that dual-core fits neatly into the hyperthreading story, but with higher performance than hyperthreaded chips because both threads are entirely independent. However, most of the headline performance issues with hyperthreading have been cache issues, where a wide-ranging housekeeping thread skips through large amounts of main memory to the extreme detriment of other processes. Dual core by itself doesn’t help here: it could be that the improved dynamic cache allocation logic in Yonah will lead to fewer severe conflicts, but that remains to be seen.

Outlook

Intel claims that the third quarter of 2006 will see two major events: the point at which dual core shipments overtake over single core, and the point at which 65nm achieves parity with 90nm. Mobile processor shipments are also increasing rapidly after languishing at around 20 percent of all processors: growth kicked off in Q2 of 2004 and is now at around 33 percent with 'not long' to go before 50 percent is reached, according to Dadi Perlmutter, general manager of Intel’s mobility division, when he talked to ZDNet UK. He also said that the company is 'at least three quarters ahead of the competition' in 65nm, and 'one to two quarters ahead' in dual core on mobile platforms.

Yonah is part of that plan. It isn’t revolutionary: battery life will be a bit longer and performance will be somewhat better, but neither will be doubled. Two cores do not equal twice the power. Nonetheless, if Yonah lives up to expectation and Intel can produce it in the quantities promised, it will be a solid indication that the company is on course for its 2010 dream of a notebook that does a day’s work on a single charge without compromising on performance. 'The competition' is mere months behind, even on Intel’s admission. In PC hardware, mobile is where the action is.

Check back for reviews of the key Napa-based business notebooks as they hit the market in the coming weeks.

| Core Duo prices (per CPU, in 1000-unit quantities) | |||

| Processor | Processor number | Clock speed (GHz) | Price |

| Core Duo | T2600 | 2.16 | $637 |

| Core Duo | T2500 | 2.00 | $423 |

| Core Duo | T2400 | 1.83 | $294 |

| Core Duo | T2300 | 1.66 | $241 |

| Core Solo | T1300 | 1.66 | $209 |

| Core Duo LV | L2400 | 1.66 | $316 |

| Core Duo LV | L2300 | 1.50 | $284 |