Intel gets ultramobile with Silverthorne debut

Intel has unveiled a slew of details on its portable and enterprise processors, new memory technologies and wireless development, as part of a 14-paper onslaught on the 2008 International Solid-State Circuits Conference, which opened in San Francisco on Sunday.

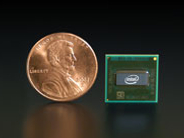

Among the details is a technical overview of Silverthorne, a brand new x86 design aimed at the portable and ultramobile market. "Silverthorne is our smallest processor since the 486, and area is proportional to the power," Justin Rattner, Intel's chief technology officer, told ZDNet.com.au's sister site ZDNet.co.uk in a pre-conference briefing.

He said Silverthorne is fully compatible with Core 2 Duo, with "hyperthreading, virtualisation and all the bells and whistles", and usable performance down to the half-watt range -- 10 times lower power than the ultra-low-voltage Dothan chip currently popular among UMPC vendors.

"The dynamic range is exciting," Rattner said. "It'll be active at under a watt but, give it a workload, and it can really crank." Silverthorne also includes a new low-power bus mode, using low-level signals, but Rattner wouldn't comment on whether Poulsbo, the chipset Intel is developing for Silverthorne, will support this. The new chip is due in the first half of 2008, he said.

Intel also unveiled its latest server chip, the Tukwila.

In other papers, Intel showed off the latest developments in phase change memory, which it is developing in conjunction with STMicroelectronics. This is planned as a replacement for flash, with data being stored in the various states of a small blob of recrystallising material.

The latest paper shows a way to store two bits per cell by holding the material in one of four states, but there's still no date set for commercialisation. Another memory technology described is dynamic memory running as fast as static memory but with twice the memory density; this two-nanoseconds access time, 128GB-per-second bandwidth design is intended for tight integration with a processor design in a many-core configuration.

With radio, the company showed a 65nm CMOS power amplifier for WiMax, 3G or WLAN use that's designed to be integrated on-chip with the rest of the circuitry. Normally analogue and off-chip, this amplifier is class E, which uses precision-timed switching at digital levels to create nearly a watt of output signal.

"Wireless radios are undergoing a very rapid series of evolutionary changes, to take us from discrete radios, largely analogue in nature, to integrated radios on a single chip doing multi-standard implementation," said Rattner. "Lots of our research is targeted at a multi-radio vision."