Intel reveals Larrabee's cores and effects

Intel has revealed further details of its Larrabee many-core processor family, saying that the first product will be configured as a graphics processor.

In a paper to be published at the Siggraph conference in Los Angeles on 12 August, the company reveals that the chip will use x86 cores based on an existing Pentium, but with in-order processing instead of the complex out-of-order designs of later chips.

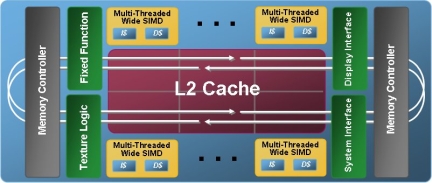

The cores work with additional vector processing units and 'fixed function logic blocks' — including a texture sampler — to support graphics and other applications. Processing elements are linked together by a shared level-2 cache — with each core getting 256KB — and two 512-bit lanes, high-speed, bi-directional ring topology bus (see Figure A). When more than 16 cores are in use, this bus is subdivided into overlapping local rings.

Although no physical or performance details have been revealed, Intel has disclosed some simulated results showing that gaming performance increases linearly from eight to 48 cores (see Figure B). For some non-gaming uses, such as Fourier transforms — a mathematical process common in signal processing — simulations show linear performance benefits up to 64 cores. However, other applications show a slowing in performance increases after 32 cores.

Each core will be capable of running four threads simultaneously, each with its own register set, while the chip as a whole will support DirectX and OpenGL APIs (application programming interfaces). A software scheduler is used to balance the load on the chip and despatch threads in an efficient manner.

The first Larrabee-based products are expected to be launched in late 2009 or early 2010. Although the initial market will be gaming, the long-term plans for the architecture include many high-performance computing applications, such as design, science and engineering.

Figure A

Figure B