The chip industry's looming 20-nanometer cliff

The chip industry is facing its own sort of cliff at 20 nanometers. What happens beyond that was the theme of the IEEE's 2012 International Electron Devices Meeting, which took place this week in San Francisco.

To some extent this is what IEDM has always been about. The end of Moore's Law has been predicted many times but the industry always finds a way forward. Intel confirmed it was using new materials--a high-k insulator and metal gates--at IEDM in 2007, and the rest of the industry eventually followed.

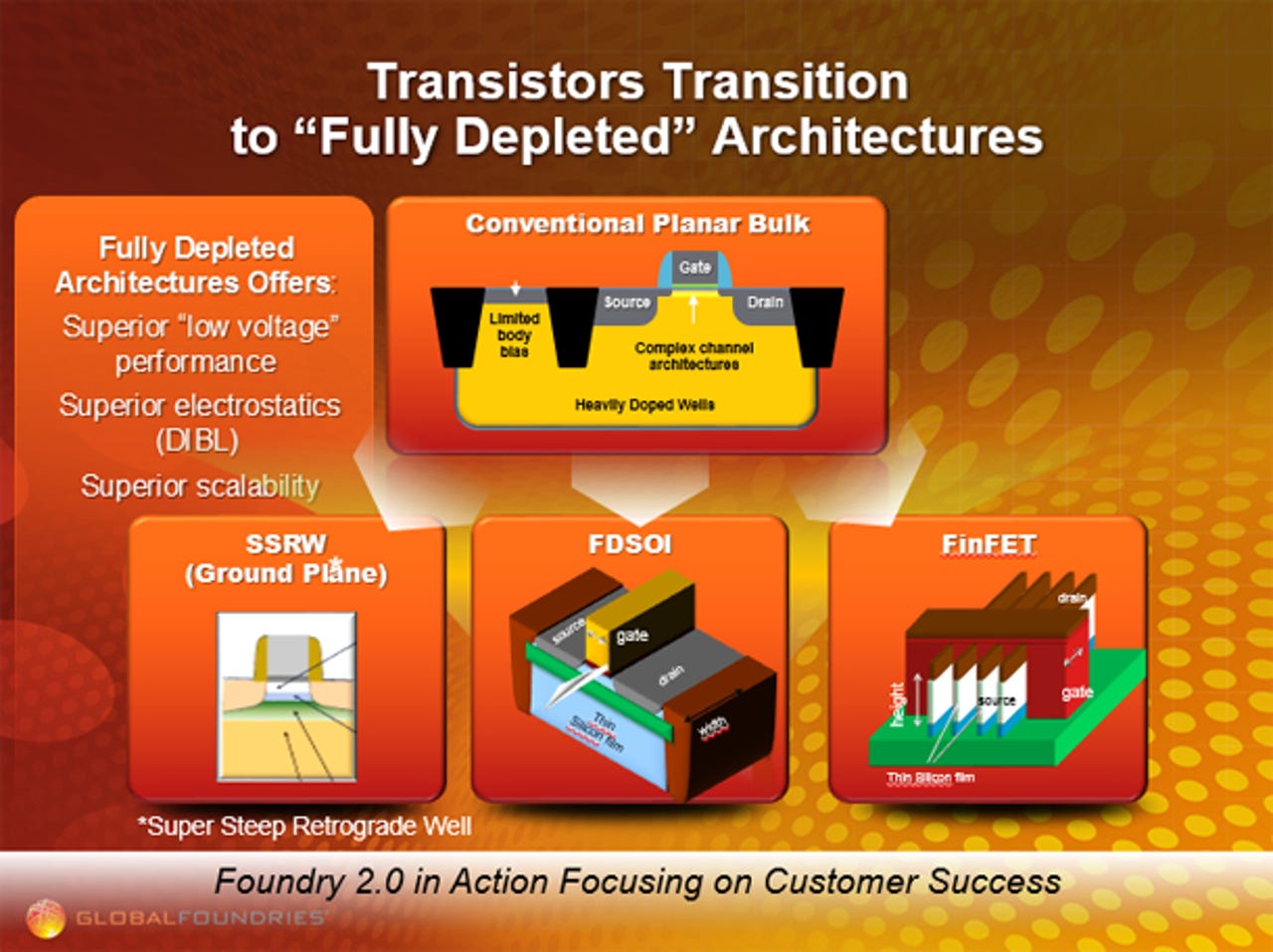

But this year felt a bit different for two reasons. First, it seems clear that Moore's Law scaling has slowed down and the basic recipe that has served the industry for so long--planar CMOS transistors on silicon wafers--really has reached the end of the road at 20nm. On that nearly everyone agrees. Second, there are still many alternatives on the table, which made this year's conference very interesting.

The front-runner is the 3D transistor or FinFET. Unlike conventional planar transistors which have a channel on the surface of the wafer and a gate on top, FinFETs have a channel that sticks up like a fin (hence the name) with a gate that wraps all the way around it for better control. Intel was the first to introduce FinFETs (the company calls them "tri-gate transistors") with its 22nm Ivy Bridge Core processors, which began shipping nearly a year ago.

The leading-edge foundries, which are currently manufacturing 28nm chips, are sticking with planar bulk CMOS through the 20nm generation, though it is unlikely to provide the same benefits as previous shrinks. After that the foundries will shift to FinFETs. In October TSMC announced that it would introduce FinFETs on a 16nm node by the end of next year followed by a 10nm node with FinFETs in early production at the end of 2015.

GlobalFoundries, which had previously said it will start production of chip with 14nm FinFETs in 2014, revealed a new roadmap at IEDM. The foundry, which manufactures most of AMD's processors, also plans to deliver 10nm in 2015 and 7nm in 2017 using FinFETs.

FinFETs now appear to be the best solution for high-performance processors found in PCs and servers and for discrete graphics. But there's a lot more debate about whether they are a also good solution for other types of chips, especially the mobile processors in tablets and smartphones, which have very different requirements. Indeed some competitors predicted Intel's 22nm technology simply wouldn’t work at all with these so-called mobile SoCs (System-on-Chip).

Seeking to put those rumors to rest, Intel presented details of its 22nm SoC platform at IEDM. In addition to high-speed logic transistors, the SoC platform uses two other families of transistors--low-power and high-voltage--to make it suitable for mobile devices. Intel said the new transistors are 20 to 65 percent faster than the ones in its current 32nm chips and will deliver longer battery life. (The company had previously disclosed some of his at the Intel Developer Forum a few months back.) As part of its strategy to catch up in mobile, Intel has previously said it plans to ship 22nm Atom SoCs next year followed by 14nm versions in 2014.

The primary alternative is a technology called FD-SOI, for Fully-Deleted Silicon-On-Insulator. Although FD-SOI can’t match the raw performance of FinFETs, proponents claim it is better suited for mobile processors, and that it is easier to design and manufacture chips using FD-SOI (though Intel would disagree with this).

STMicroelectronics is the biggest backer of FD-SOI, which it plans to use to manufacture ST-Ericsson's NovaThor ModAp processors, but GlobalFoundries and IBM will also offer FD-SOI. At IEDM, STMicroelectronics announced that its 28nm FD-SOI technology is now ready for "pre-production." A NovaThor SoC with a multi-core Cortex-A9 processor and integrated cellular radios, manufactured with 28nm FD-SOI, will deliver either 30% better performance at the same power or 30% lower power at the same speed, in comparison to a convention 28nm low-power process, the company claims. The FD-SOI camp plans to skip 20nm altogether and offer a 14nm version in 2014--around the same time 14nm FinFETs are available--and 10nm FD-SOI in 2016. All of these use planar transistors, but IBM is also planning to use a recipe that combines FinFET transistors with an SOI substrate starting at 14nm. It claims this 3D-FD will scale all the way down to 5nm.

A third option, a deep or retrograde well used to tweak the electrical performance of transistors, is also in the running. This doesn't provide the same benefits in terms of performance or power as other methods of scaling, but it may be a way to extend existing planar bulk technology at relatively low cost. GlobalFoundries plans to offer SSRW, or Super-Steep Retrograde Wells, and start-up SuVolta has its own version of this, known as Deeply Depleted Channel (DDC) technology. At IEDM, SuVolta announced that Fujitsu had used DDC on analog and digital circuits manufactured on a 65nm process to boost performance and reduce power. The companies said the technology will be commercially available at 55nm in the first half of 2013, but of course this won’t really help at 20nm and beyond.

The final option for the industry is to try to just keep on doing what it has been doing rather than resorting to entirely new structures. At IEDM IBM gave details on its latest 22nm process for high-performance server and game console chips, and said that the frequency continues to scale at the same rate. And Samsung gave a talk on the prospect for pushing planar transistors below 20nm as a way to cut costs.

But it seems clear that 20nm is an inflection point for chipmakers. So why does all this matter? The drive for greater capabilities in laptops, tablets and smartphones--better performance, higher resolution displays, faster data rates--demands ever more powerful chips. But batteries aren't getting much better, which means chipmakers will have to find ways to stay on Moore's Law to make it happen. The challenges at 20nm seem formidable, but as in the past, it looks like the industry will come up with solutions to get us through at least the next several generations.