Intel shows 48-core 'datacentre on a chip'

Intel has announced the Single-chip Cloud Computer (SCC), an experimental 48-core processor designed to encourage research and development in massively parallel computation.

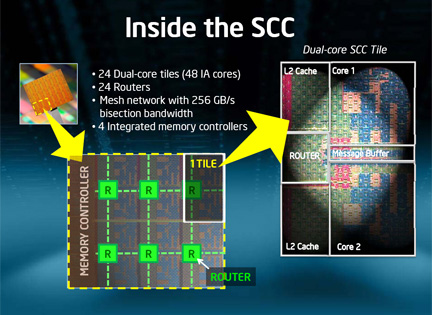

Measuring 567 square millimetres — about the size of a postage stamp — the SCC combines 24 dual-core processing elements, each with its own router, four DDR3 memory controllers capable of handling up to 8GB apiece, and a very fast on-chip network.

Although no performance, speed or total bandwidth figures were revealed, the chip has 1.3 billion transistors, consumes up to 125 watts in operation, and will become available to researchers around the world on a standard-sized motherboard in the first half of 2010. Intel said it expects to sign up dozens of partners within six months, with more to come over time.

"This is the prototype of the microprocessor of the future", Joseph Schütz, director of microprocessor and programming research at Intel Labs, said on Tuesday. The announcement took place at the company's R&D centre in Braunschweig, Germany, at the first of three SCC launch events around the world. "Before, if you needed to design software for this level of computing, you needed your own datacentre. Now, you just need your own chip," said Schütz.

The SCC, previously code-named Rock Creek, is fabricated in 45nm technology. The on-chip network is configured as a 6x4 node, two-dimensional mesh. It has a bandwidth of 256GBps, and each core can run its own independent software as a fully functional IA-32 processor.

Memory, 384KB of it, is shared between all cores, primarily to speed message passing, while power management can independently control eight variable-voltage and 28 variable-frequency areas of the chip. This controls power consumption, setting it between 25 and 125 watts.

"We called it the Single-chip Cloud Computer, but it was very difficult to know how to name it", said Schütz. "You can easily envision many more cores, just as you could add more servers to a real datacentre. We could build relatively small systems with hundreds or thousands of cores."

Unlike other manycore systems, the SCC does not maintain data integrity through cache coherency, where special circuitry keeps multiple caches in sync across cores.

"Cache coherency consumes a lot of power but isn't that useful," said Schütz. "You're tempted to do it because you're on one die, but as soon as you go off-die, it doesn't work. This is a slice of the future in silicon, and we're giving to people to play with."

Microsoft, a partner in the SCC project, has built support into its developer toolchain, according to Schütz.

Professor Timothy Roscoe of ETH Zurich, who is developing the experimental Barrelfish operating system also in conjunction with Microsoft, told ZDNet UK that the SCC was a particularly good fit for his work.

"Our multikernel architecture has many independent processors with different attributes, but sharing the same state", he said, "and the SCC looks a dream platform for testing many of our ideas".

Intel said it will publish full details of the SCC at the International Solid-State Circuits Conference in San Francisco on 8 February, 2010.