AMD realigns two-year plan around 'ambidextrous computing'

After more than two years in the making with a foundation in "skybridge" technology, AMD pulled back the curtain on its "ambidextrous architecture."

Speaking during a press conference at the Ritz-Carlton in San Francisco on Monday morning, AMD CEO Rory Read reflected that when he joined the processor maker five years ago, approximately 95 percent of the company's business centered around PCs.

Since then, Read said that AMD embarked on a new strategy, starting approximately three years ago, to unlock its own intellectual property for the "cloud era," starting by integrating graphics and design resources.

By 2015, Read projected that 50 percent of AMD's revenue will come from these "high-growth" segments.

Lisa Su, senior vice president and general manager of AMD's global business, explained further that hitting the goals start with satisfying the consumer. That means smartphones, tablets, and more along those lines.

"It's not just words driving all of that content," Su warned, but all of the video, graphics, and more.

But it also reshapes the datacenter, Su continued, as well as silicon architectures need to power the entire platform.

For 2015, AMD is aiming to bring in new markets that can benefit from ambidextrous computing.

"We believe in the total compute story," Su said, "And it's just going to expand with our ambidextrous vision."

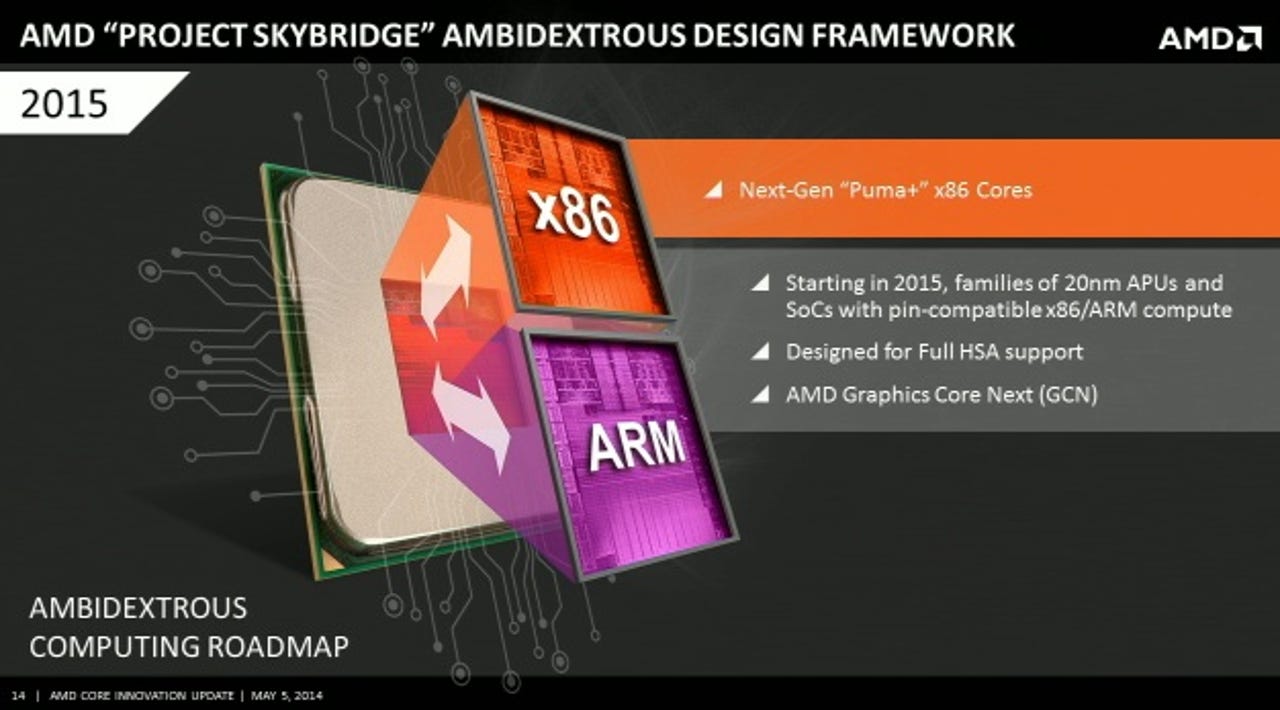

To accomplish this, AMD unveiled Project Skybridge, a design framework with a family of products headed toward a variety of marketplaces to help customers innovate and reduce time-to-market.

Su touted that this is the first time that x86 and ARM SoCs have been put together in a way that they are "pin-compatible," meaning a motherboard that runs both. Skybridge will also produce AMD's first ARM-based chips supporting Android.

The first Skybridge products will use 20nm process technology with Puma+ APUs scheduled to roll out in 2015.

Going back to Read's description of "ambidextrous" computing, Su posited that AMD is the "only company" capable of briding ARM and x86 systems. She further touted that this strategy will contribute roughly 80 percent of revenue share, or $80 billion, in 2014.

"The bridge to the future is offering both ARM and x86 in our portfolio," Su asserted, highlighting AMD's debut of a 64-bit ARM server processor, code-named Seattle, last year.

AMD executives offered the first public demonstration of Seattle during Monday's presentation, noting support for everything from social media to storage to big data applications.

For this particular demo, AMD honed in on web hosting, shining the spotlight on popular blogging software WordPress as one example of a heavily-trafficked host with users worldwide trying to keep millions upon millions of webpages online at all times.

The initial takeaway from the brief demonstration was that Seattle enables programmers to be able to extract information from the server and create web pages (or rather, a "complete" web hosting solution with interactive video, etc.) on the fly.

Hewlett-Packard is another customer already taking advantage of AMD's Seattle platform.

Paul Santeler, vice president and general manager of HP's hyperscale unit, predicted to see ARM focus on new datacenter spaces, listing off a number of requirements that need to be met first in terms of volume economics as well as hardware and software ecosystems.

Next-generation, scale-out datacenters, Santeler observed, are "very homogenous" as they get new users and software developers to match while continuously adopting new technologies.

Su followed up by positing there is a "new opportunity for disruption here with ARM."

Su concluded that the "final piece of the puzzle" in AMD's two-year roadmap is serving as an ARM architecture licensee with development of its own ARM cores already in process.

"We believe in the total compute story," Su said, "And it's just going to expand with our ambidextrous vision."

Screenshots via AMD Investor Relations